Table of Contents

- Introduction: The Perfect Chip Myth

- The Fabrication Problem: What Goes Wrong in a Superconducting Chip

- Dropouts in the Surface Code: The Error Correction Perspective

- Google's Work on Qubit Dropouts: LUCI and Beyond

- The Noise Model Zoo: Dropout vs. Noise

- Generalising to Other Hardware Modalities

- Cross-Platform Comparison: A Unified View

- The Deep Connection: Erasure, Loss, and Percolation

- Open Challenges and Outlook

- Conclusion

- References

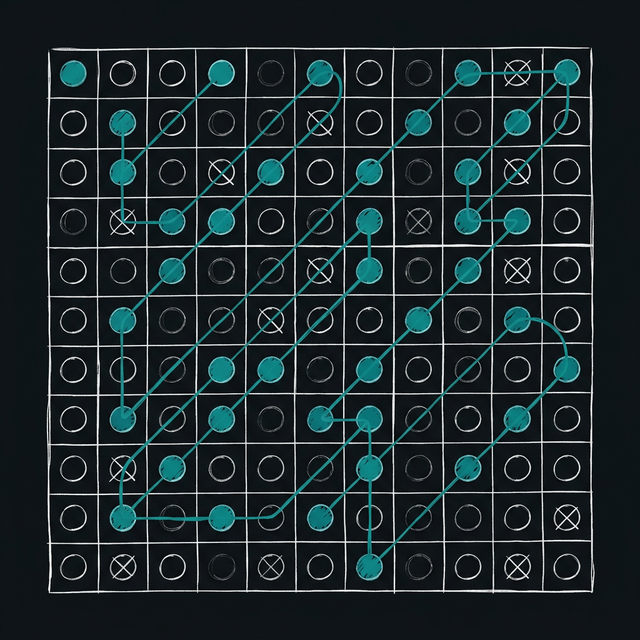

Visualizing the reality of a modern quantum processor: a minimalist sketch showing a lattice where some nodes are missing from the start.

Introduction: The Perfect Chip Myth

Let me set the scene. You have just spent three months carefully designing a 100-qubit superconducting processor. The lithography looks perfect under the microscope. The Josephson junctions are fabricated, the coplanar waveguide resonators are tuned, and the dilution fridge is humming along at 10 mK. You do a first round of spectroscopy — and then the unpleasant reality hits: maybe 5–10 of your 100 qubits are just... broken. They either have wildly wrong frequencies, they decay in nanoseconds rather than microseconds, or they won't couple to their neighbours at all. Welcome to the world of qubit dropouts.

This is not a niche problem. It is, in fact, one of the most practically important challenges separating a working quantum processor from a large-scale fault-tolerant quantum computer. In classical semiconductor fabrication, transistor yield is above 99.99%. In contrast, the operational yield of superconducting quantum chips — defined as qubits that meet all performance thresholds after packaging and calibration — currently runs 40–60% lower than raw fabrication yield across the industry [8]. That gap is enormous.

In this post, I want to explore this problem from the ground up. I will start with the physical origins of fabrication-induced imperfections in superconducting chips, explain what makes a qubit "drop out" either permanently or temporarily, and then dive deep into how quantum error correction (QEC) — particularly the surface code — can handle these dropouts. I will pay special attention to the remarkable work from Google Quantum AI's LUCI framework and their Willow chip. I will then generalise the discussion to other hardware modalities — trapped ions, neutral atoms, photonic qubits, and silicon spin qubits — and map out how each one has its own flavour of this dropout problem.

What is a Qubit Dropout?

A dropout is any qubit or coupler that is either permanently or temporarily unusable within the context of a quantum error correction protocol. This includes qubits that are non-functional due to fabrication defects, as well as those transiently degraded by drifting material defects or external perturbations.

The Fabrication Problem: What Goes Wrong in a Superconducting Chip

A Quick Anatomy of a Superconducting Transmon Qubit

Before diving into what goes wrong, let me briefly outline what is supposed to go right. A transmon qubit [1] is essentially a nonlinear LC oscillator. The nonlinearity comes from a Josephson junction (JJ) — two superconducting electrodes separated by a thin aluminium oxide (AlOx) tunnel barrier, typically 1–2 nm thick. The qubit frequency is set by the junction's Josephson energy \(E_J\) and the shunting capacitance \(C_s\):

where \(E_C\) is the charging energy and \(C_\Sigma\) is the total capacitance. Typical qubit frequencies sit in the 4—7 GHz range. The anharmonicity — the energy difference between the \(|1\rangle \to |2\rangle\) and \(|0\rangle \to |1\rangle\) transitions — is approximately \(-E_C/\hbar\), keeping the qubit addressable.

The key point is that \(E_J\) is exquisitely sensitive to the tunnel barrier thickness. A \(\sim\)10% variation in oxide thickness changes the Josephson energy, shifts the qubit frequency, and can push it into resonance with a neighbour qubit or a spurious material defect. This is the microscopic origin of much of the chip-to-chip variability in superconducting processors.

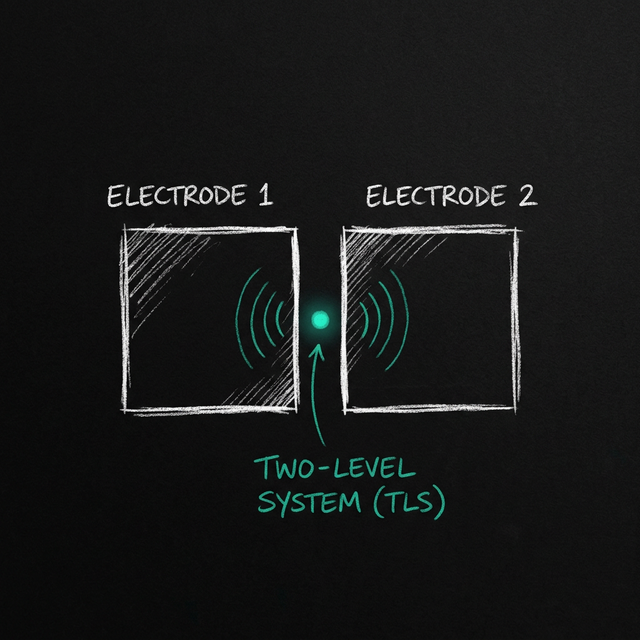

Two-Level System Defects: The Silent Killers

The single most important fabrication-induced noise source in superconducting qubits is the two-level system (TLS). These are quantum mechanical defects — atomic-scale tunnelling systems in amorphous materials — that parasitically couple to the qubit and rob it of coherence [2, 3].

TLS defects arise from several locations:

- The JJ tunnel barrier: The amorphous AlOx is a glassy material riddled with structural defects. TLSs in the barrier couple to the qubit via charge fluctuations, generating both \(T_1\) relaxation (energy loss) and \(T_2\) dephasing (phase randomisation) [4].

- Electrode surfaces and interfaces: Roughly 46% of all TLS defects have been localised on the surface of the qubit chip, and 10% at the metal–substrate interface [5].

- The Josephson junction leads: A recent breakthrough technique using on-chip gate electrodes to map individual TLS positions found that the majority of surface-TLS cluster specifically on the leads of the Josephson junction, in regions fabricated by shadow-evaporation and lift-off techniques [6]. This indicates that the fabrication process itself, not just the oxide, is a primary TLS generator.

The effect of a resonant TLS on a qubit is dramatic. When a TLS resonance frequency drifts into alignment with the qubit frequency — something that happens stochastically as TLS energies fluctuate with local charge or strain — the qubit \(T_1\) can drop by orders of magnitude in minutes. This is what experimentalists often call a "glitch" event, and it is a well-known headache in any superconducting lab.

Figure 1. Technical sketch of a Josephson junction showing a single Two-Level System (TLS) defect in the tunnel barrier.

Other Fabrication-Induced Failure Modes

TLS are not the only villain. Several other fabrication imperfections contribute to qubit dropouts:

- Frequency collisions:

- Since qubit frequencies depend sensitively on JJ critical currents, fabrication spread causes a distribution of qubit frequencies. If two neighbouring qubits land at the same frequency, they become permanently entangled in an uncontrolled way — effectively rendering one (or both) inoperable.

- Coupler failures:

- In architectures like Google's Sycamore and Willow, tunable couplers are placed between every pair of data qubits. A coupler with a defective SQUID loop cannot be tuned to the correct working point, severing the connection between neighbouring qubits.

- Quasiparticle poisoning:

- Trapped non-equilibrium quasiparticles (QPs) act as a distinct type of TLS, coupling to the qubit junction and causing relaxation [7]. QP generation can be triggered by external radiation or residual microwave power.

- Substrate-induced losses:

- The sapphire or silicon substrate itself can host surface oxides and adsorbates that couple to the qubit's electric field. Techniques like partially suspending superinductors in air aim to eliminate this source.

The Operational Yield Gap

Vendors frequently advertise "99% fabrication yield," meaning 99% of qubits survive the manufacturing line. However, operational yield — qubits that meet all performance thresholds (frequency, \(T_1\), \(T_2\), gate fidelity) after packaging — runs 40–60% lower than this fabrication yield [8]. For large-scale quantum computing, this gap is a critical engineering challenge.

Dropouts in the Surface Code: The Error Correction Perspective

Surface Code Basics

Let me briefly recap the surface code, since everything else in this section depends on it. The surface code encodes one logical qubit into a 2D array of \(d \times d\) data qubits surrounded by \((d^2-1)\) ancilla (measure) qubits [9]. The code corrects any error acting on fewer than \(\lfloor d/2 \rfloor\) qubits.

Error detection works by repeatedly measuring the stabilisers (plaquettes). A violated stabiliser gives a nonzero syndrome bit, and the pattern of syndrome bits is fed to a classical decoder that infers the most likely error chain and applies a correction.

Surface Code Distances

- Spacelike distance: Minimum weight of a logical operator crossing boundaries. Governs protection against spatial errors.

- Timelike distance: Minimum weight of a logical operator connecting rounds. Governs protection against measurement errors.

Dropouts reduce effective distances below the nominal \(d\).

Why Dropouts Break the Surface Code

Imagine a distance-9 surface code on a perfect \(9 \times 9\) grid. Now one qubit is broken — it simply does not exist. This has immediate consequences:

- The stabilisers adjacent to the missing qubit are now weight-3 (missing one leg) rather than weight-4. They still commute but are weaker.

- A logical error chain can now route around the missing qubit, passing through fewer qubits. The effective spacelike distance is reduced.

- If the missing qubit is a measure qubit, the stabiliser it was supposed to measure is entirely absent, creating a "blind spot" in the syndrome extraction.

In the literature, there is a beautiful mapping between qubit loss on the surface code and a percolation transition [10]. If each qubit is independently removed with probability \(p_{loss}\), the logical information survives as long as there exists a connected path of intact qubits. This maps to the bond-percolation threshold \(p_c \approx 0.5\). However, real dropouts are not random, and realistic thresholds are much lower.

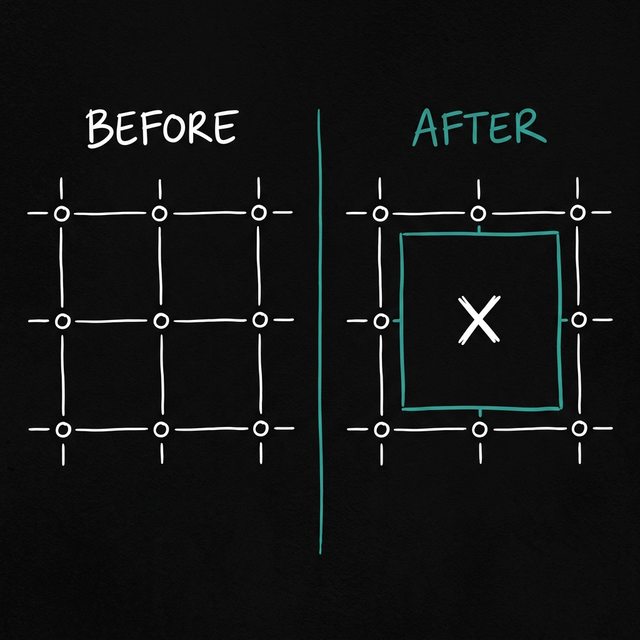

The Superplaquette Approach: Bridging the Gap

The first systematic approach to handling static qubit losses was the superplaquette construction [11]: If a data qubit is missing, merge the surrounding plaquettes into one large "superplaquette."

Figure 2. Minimalist diagram showing how a missing qubit leads to the formation of a 'superplaquette' in the surface code lattice.

Numerical simulations with circuit-level noise showed that at 95% functional qubit yield, a large-scale quantum computer is buildable. At 90% yield, it's still usable with chip selection. But at 80% yield, error suppression is insufficient even after discarding most chips.

Google's Work on Qubit Dropouts: LUCI and Beyond

Motivation: Sycamore, Willow, and the Yield Problem

Google's Sycamore and Willow processors use a grid of transmon qubits connected by tunable couplers. In these architectures, both broken data qubits and broken couplers constitute dropouts. A broken coupler is particularly problematic because in the naive approach, one typically removes the data qubit connected via that coupler from the code, losing more code distance than strictly necessary.

In prior methods (the Auger/Bandage method [13] and the Strikis/Brown method [14]), an isolated broken coupler reduced the distance by cutting out the adjacent data qubit, and an isolated broken measure qubit reduced spacelike distance by two. These penalties accumulate rapidly in a large chip.

The LUCI Framework

In late 2024, Google Quantum AI published LUCI [11]. The key insight behind LUCI is to abandon the traditional circuit construction and instead work from the mid-cycle state of the surface code as a "home base." Circuits are then constructed as sequences of rounds, each starting and ending at this mid-cycle state.

Detecting Regions

The theoretical underpinning comes from the framework of detecters [12]: space-time volumes in the circuit over which a stabiliser is "alive." By thinking about QEC circuit construction as covering all circuit locations with detecting regions (rather than building explicit gates for a static code), new circuit topologies become accessible.

LUCI's Core Promise

For isolated broken couplers or isolated broken measure qubits, LUCI preserves spacelike distance at the cost of halving timelike distance relative to the standard surface code. For broken data qubits, spacelike distance is reduced by 1 (vs. 2 for prior methods).

Performance Numbers

Let's look at the concrete numbers for a benchmark scenario (1% qubit and coupler dropout, patch diameter 15):

| Method | Avg. Spacelike Distance | Logical Error Rate Improvement |

|---|---|---|

| Strikis/Brown | 9.1 | 1× (baseline) |

| Auger/Bandage | 9.1 | 1× (baseline) |

| LUCI | 13.1 | 36× improvement |

LUCI also improves resource efficiency: to reach a "teraquop" target (logical error probability of \(10^{-12}\)), LUCI requires approximately 25% fewer physical qubits than the Auger/Bandage method at the same dropout rate [11].

Google Willow: Below-Threshold Error Correction

In December 2024, Google published results in Nature showing that their 105-qubit Willow chip achieved below-threshold operation of the surface code for the first time [15]:

- A distance-7 code across 101 physical qubits achieved \(\Lambda = 2.14 \pm 0.02\).

- Logical error rate of \(0.143\% \pm 0.003\%\) per error-correction cycle.

- The logical qubit's coherence lifetime surpassed the best physical qubit by a factor of 2.4×.

Key to achieving this was the transition to a dedicated fabrication facility which enhanced qubit performance to coherence times averaging 68 \(\mu\)s [16]. LUCI and Willow are two sides of the same coin — one improves hardware, the other makes QEC robust to remaining imperfections.

Dynamic Surface Codes

In late 2025, Google's team demonstrated dynamic surface code implementations on the Willow chip [17]. These include a hexagonal-lattice code and a "walking" surface code that periodically swaps qubit roles. By moving away from rigid, statically assigned roles, one gains the freedom to route around broken components more effectively.

The Noise Model Zoo: Dropout vs. Noise

Before generalising, let me be precise: not all imperfections are created equal. The key insight is that the more information available about where and when an error occurred, the easier it is to correct.

| Error Type | Description | Decoder Strategy |

|---|---|---|

| Pauli errors | Random \(X, Y, Z\) flips | Standard MWPM |

| Erasure errors | Error at known location/time | Simplified "filling" decoding |

| Static dropouts | Permanently missing; known at compile time | LUCI / Superplaquettes |

| Correlated bursts | Many qubits fail at once (cosmic rays) | Special burst-detection [18] |

| Leakage | Population escapes qubit subspace | Leakage reduction units (LRUs) |

Erasure Qubits: Converting Unknowns to Knowns

An erasure qubit is engineered so that when it fails, it signals the failure. In the erasure error model, a distance-\(d\) code can correct up to \(d-1\) erasures — double the capacity for Pauli errors at the same distance [20]. In 2024, Levine and Painter (Amazon/Caltech) demonstrated the first erasure qubit using a dual-rail encoding where photon loss is detectable [21].

Generalising to Other Hardware Modalities

The qubit dropout problem exists in every hardware modality, but the physical origin and the dominant noise model vary dramatically.

Trapped-Ion Quantum Computers

Trapped ions do not have the same TLS problem as superconducting qubits. The ions themselves are perfect, identical quantum systems. The fabrication challenge is in the ion trap. Key imperfections include motional (anomalous) heating from the trap electrodes [22] and optical crosstalk in large arrays.

A "dropout" in trapped ions occurs if an ion is lost from the trap (collision with background gas) or leaks out of the computational subspace via spontaneous emission. Metastable ion qubits can convert spontaneous emission errors into detectable erasures with high efficiency [24].

Neutral-Atom Arrays

Neutral atoms in optical tweezers are loaded stochastically. Atom loss is the primary imperfection, occurring during loading or due to background gas collisions. This is a known erasure if detected in real time. Adaptive decoding leveraging known loss locations can improve logical error rates by orders of magnitude [26]. Furthermore, atoms can be replenished mid-circuit without disturbing the computation.

Photonic Quantum Computing

In photonic computing, the ultimate dropout is photon loss. A lost photon is the most natural erasure error. The Fusion-Based Quantum Computation (FBQC) architecture is designed specifically for this, with loss thresholds reaching ~10% per fusion [28]. In 2025, PsiQuantum demonstrated a manufacturable silicon-photonics platform bringing FBQC close to fault-tolerance thresholds [30].

Silicon Spin Qubits

Silicon spin qubits are exquisitely sensitive to fabrication. Valley splitting disorder caused by interface roughness can make a qubit leak into the wrong valley state [31]. Charge noise from interface traps leads to dephasing [32]. A site with low valley splitting effectively drops out, requiring leakage reduction units to manage.

Cross-Platform Comparison: A Unified View

The following table summarizes the dropout signatures across different platforms. The key pattern is that the more erasure-like the dominant error, the more efficient QEC becomes.

| Platform | Primary Failure | Erasure Fraction | QEC Strategy |

|---|---|---|---|

| Superconducting | TLS, Collisions, Broken Couplers | Low | LUCI, Superplaquettes |

| Trapped Ion | Ion loss, Spontaneous emission | High (Metastable) | Erasure-conversion |

| Neutral Atom | Atom loss | Medium-High | Superchecks, Replenishment |

| Photonic | Photon loss | Very High | FBQC fusion networks |

| Silicon Spin | Valley leakage, Charge noise | Low | LRUs, Dynamical decoupling |

The Deep Connection: Erasure, Loss, and Percolation

There is a beautiful unification between qubit loss and the percolation threshold [10]. For the 2D surface code, the bond percolation threshold is \(p_c = 0.5\), meaning half of all qubits can be randomly removed before the logical qubit is lost. LUCI's contribution is to extract as much remaining code distance as possible from an imperfect chip, bringing the effective distance \(d_{\text{eff}}\) as close to the ideal \(d\) as possible.

where \(p_{\text{drop}}\) is the dropout fraction and \(\alpha\) is a geometry-dependent coefficient that LUCI successfully minimises.

Open Challenges and Outlook

Despite progress, hurdles remain: correlated dropouts (spatially clustered defects or cosmic ray bursts [35]); scaling to 10× lower physical error rates; and achieving sub-microsecond latency for real-time circuit adaptation around transient TLS glitches. The future lies in noise-tailored codes and erasure qubit engineering.

Conclusion

The journey from a fabricated chip to a fault-tolerant logical qubit is paved with glitches. These are not just engineering inconveniences but deep physical phenomena connecting condensed matter to information theory. Google's LUCI framework is a landmark response: redesigned circuits that route around broken components while preserving code distance. As we scale to millions of qubits, the interplay between fabrication quality and adaptive QEC will only grow more central. The real work has only just begun.

References

- J. Koch et al., "Charge-insensitive qubit design derived from the Cooper pair box," Phys. Rev. A 76, 042319 (2007).

- L. V. Abdurakhimov et al., "Identification of high-frequency defects in superconducting qubits," PRX Quantum 3, 040332 (2022).

- J. Lisenfeld et al., "Decoherence spectroscopy with individual two-level tunnelling defects," Sci. Rep. 6, 23786 (2016).

- L.-C. Ku and C. C. Yu, "Decoherence of a Josephson qubit due to coupling to two-level systems," Phys. Rev. B 72, 024526 (2005).

- J. Lisenfeld et al., "Resolving the positions of defects in superconducting quantum bits," Sci. Rep. 9, 3982 (2019).

- "Mapping the positions of noisy defects on a superconducting qubit," arXiv:2511.05365 (2025).

- S. E. de Graaf et al., "Two-level systems due to trapped quasiparticles," Science Advances 6, eabc5055 (2020).

- SpinQ, "Quantum chip procurement guide: 3 yield traps vendors hide," SpinQuanta Blog (2025).

- A. G. Fowler et al., "Surface codes: Towards practical large-scale quantum computation," Phys. Rev. A 86, 032324 (2012).

- T. Botzung et al., "Robustness and measurement-induced percolation of the surface code," J. Phys. A 58, 205304 (2025).

- D. M. Debroy et al., "LUCI in the surface code with dropouts," Quantum 9, 1936 (2025).

- M. McEwen et al., "Relaxing hardware requirements for surface code circuits," Quantum 7, 1172 (2023).

- J. M. Auger et al., "Fault-tolerance thresholds for the surface code with fabrication errors," Phys. Rev. A 96, 042316 (2017).

- A. Siegel et al., "Adaptive surface code for quantum error correction," Quantum 7, 1065 (2023).

- Google Quantum AI, "Quantum error correction below the surface code threshold," Nature 638, 920 (2025).

- M. Eichinger, "What made the leap from Sycamore to Willow possible?" LinkedIn (2025).

- M. McEwen et al., "Demonstration of dynamic surface codes," Nature Physics 21, 1994 (2025).

- S. J. S. Tan et al., "Resilience of the surface code to error bursts," arXiv:2406.18897 (2024).

- H. Levine et al., "Demonstrating a long-coherence dual-rail erasure qubit," Phys. Rev. X 14, 011051 (2024).

- "Erasure qubits in quantum error correction," Emergent Mind (2026).

- H. Levine, O. Painter et al., PRX 14, 011051 (2024).

- K. Lakhmanskiy et al., "Argon Ion Treatment of Multi-Material Layered Surface-Electrode Traps for Noise Mitigation," Entropy 27, 1208 (2025).

- Z. D. Romaszko et al., "Engineering of microfabricated ion traps," Nature Reviews Physics 2, 285 (2020).

- M. Kang et al., "Quantum error correction with metastable states of trapped ions," PRX Quantum 4, 020358 (2023).

- "Researchers demonstrate quantum computations with protected logical qubits," The Quantum Insider (2026).

- H. Perrin et al., "Quantum error correction resilient against atom loss," Quantum 9, 1884 (2025).

- D. Bluvstein et al., "Logical quantum processor based on reconfigurable atom arrays," Nature 626, 58 (2024).

- S. Bartolucci et al., "Fusion-based quantum computation," Nature Comms 14, 912 (2023).

- M. L. Chan et al., "Tailoring fusion-based photonic quantum computing," PRX Quantum 6, 020304 (2025).

- PsiQuantum, "A manufacturable platform for photonic quantum computing," Nature 631, 337 (2025).

- M. P. R. Losert, "Valley splitting for spin qubits in Si/SiGe," PhD thesis (2024).

- B. Paquelet Wutz et al., "Reducing charge noise in quantum dots," Nature Comms 14, 1385 (2023).

- E. J. Connors et al., "Charge-noise spectroscopy of Si/SiGe quantum dots via dynamically-decoupled exchange oscillations," Nature Communications 13, 940 (2022).

- G. Cheng and J. Guo, "Noise correlation in silicon spin qubits," IEEE QCE (2024).

- X. Li et al., "Cosmic-ray-induced correlated errors in superconducting qubit array," Nature Comms 16, 4768 (2025).

- O. Higgott and C. Gidney, "Improved decoding of circuit noise," Quantum 7, 1060 (2023).